パスコンの最適化設計手法【LTSpice】

この記事では、LTSpiceを使用したパスコンの最適化手法について紹介します。

動画はこちら↓

パスコンとは

バイパスコンデンサ(通称パスコン)は、半導体ICの電源ラインに重畳するノイズに対して、バイパス経路を提供する役割を持ちます。

パスコンの役割については、以下の記事で解説しています。

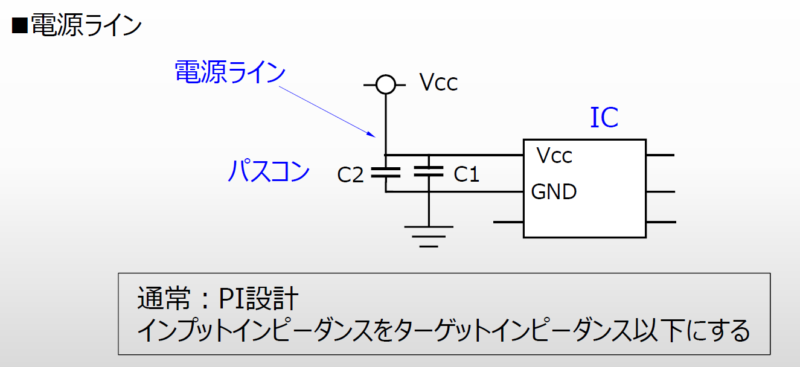

そして電源ラインのデカップリング回路においては、電源品質(パワーインテグリティ)の観点から、ターゲットインピーダンス以下となるように設計することが重要になります。

パワーインテグリティ解析の課題

パワーインテグリティ(PI:Power Integrity)が電源ラインのノイズ対策において重要であることは間違いありません。

出典:EMC設計イノベーション

出典:EMC設計イノベーションしかし、回路設計のワークフローに取り入れるためには、専用のPI設計ツールが必要となります。

このPI設計ツールには「PDN Analyzer」「PI Stream」「PIPro」などが存在しますが、これらはいずれも有償のソフトウェアになります。

そのためパワーインテグリティの重要性が理解できたとしても、一般的な回路設計者にとっては、実際の設計業務において中々手が出せないというのが実情です。

PD適用とは

そうした状況下において、PI設計ツールを使わずともパワーインテグリティ解析を行うための手法が「PD適用」です。

このPD適用では、無料の回路シミュレータである「LTSpice」を使って電源ラインのデカップリング回路を設計します。

もちろん専用のPI設計ツールと違って簡易的な解析となりますが、モデルをきちんと作り込むことで、実務レベルにおいて十分な精度でシミュレーションすることが可能です。

減衰量

PD適用の基本的な考え方はPI設計を踏襲していますが、ターゲットインピーダンスではなく、減衰量 PD をもとにデカップリング回路を設計していきます。

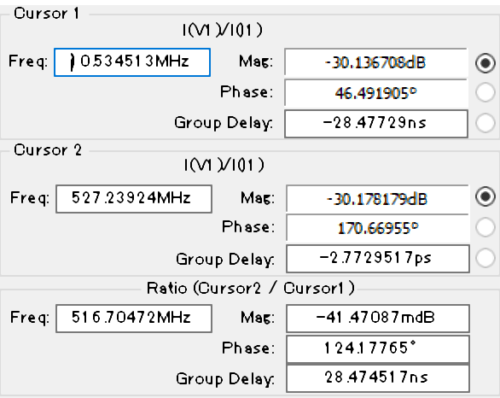

そしてこの減衰量が、PI設計で言うところのターゲットインピーダンスに相当し、おおよそ30dBというのが1つの目安になります。

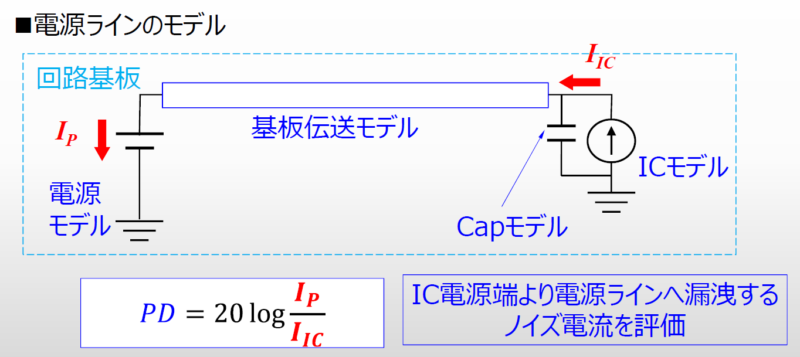

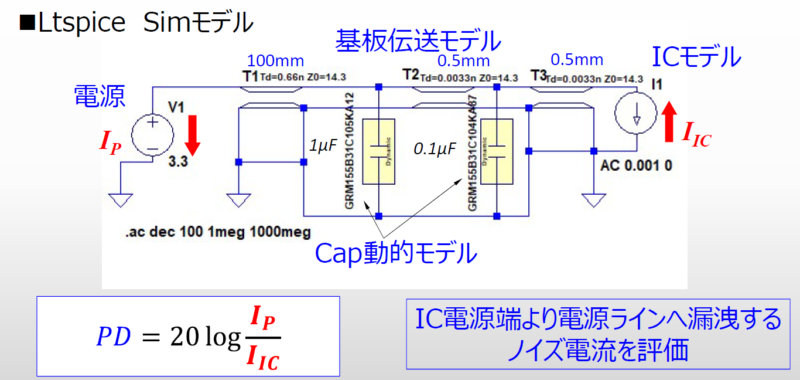

なお減衰量は、半導体ICに流れる電流 Iic と定電圧電源に流れる電流 Ip の比を取ることで求められ、デシベルで表示する場合には 20*Log(Ip/Iic) として計算できます。

出典:EMC設計イノベーション

出典:EMC設計イノベーションシミュレーションモデル

基本的なモデルの構成としては、半導体ICを模擬した電流源、デカップリング回路、定電圧電源で構成されます。

このうちデカップリング回路は、コンデンサと伝送線路モデルによって表され、これらのモデルを組み合わせることで、様々なパターンのデカップリング回路を検証できます。

出典:EMC設計イノベーション

出典:EMC設計イノベーションコンデンサのモデル

なおコンデンサは、動的モデルを使用することでより正確にデカップリング性能を解析することができます。

動的モデルの使用方法は、下記の記事で解説しています。

伝送線路のモデル

LTSpiceでは、伝送線路モデルとして「Tline」という素子を使用します。

このTlineは、線路長に相当する「遅延時間」と「特性インピーダンス」によって特性を規定することが可能で、このパラメータによって基板の寄生インダクタンスや寄生キャパシタンスを考慮してシミュレーションできるようになります。

なお遅延時間については、波長短縮の影響を受けることに注意が必要です。

パスコンの最適化シミュレーション

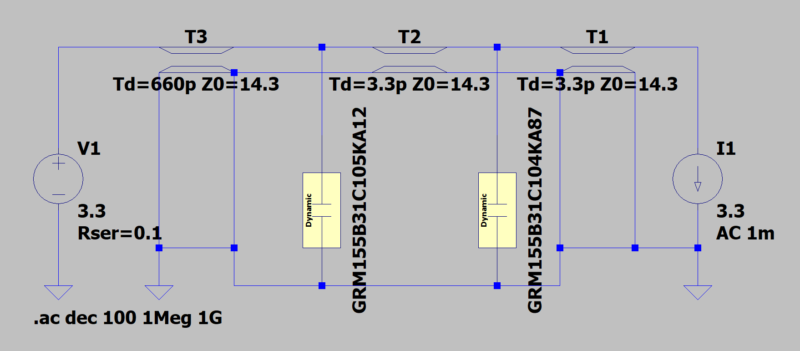

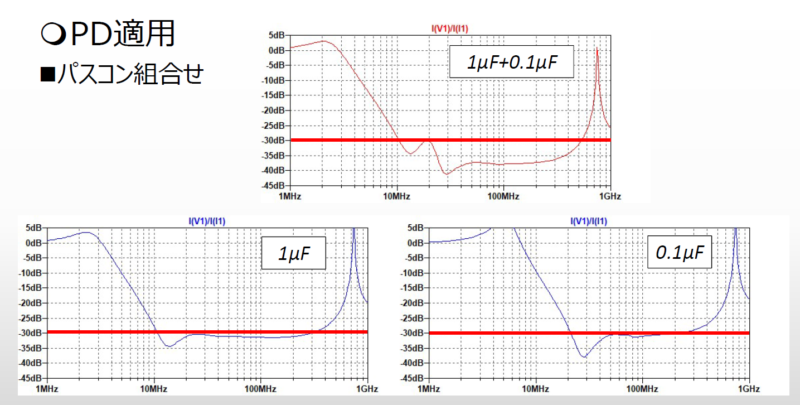

ここでは 1005サイズのセラミックコンデンサ(0.1uFと 1uF)を使用したデカップリング回路でシミュレーションしています。

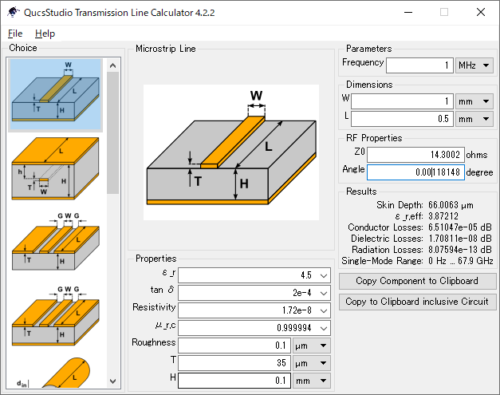

伝送線路については、特性インピーダンスを14.3Ω、遅延時間を 3.3psと 660psに設定しています。

この特性インピーダンスや遅延時間の計算については、同じく無料の回路シミュレータである「QucsStudio」の「Transmission Line Culculator」を使用すると便利です。

QucsStudioのダウンロード方法はこちら。

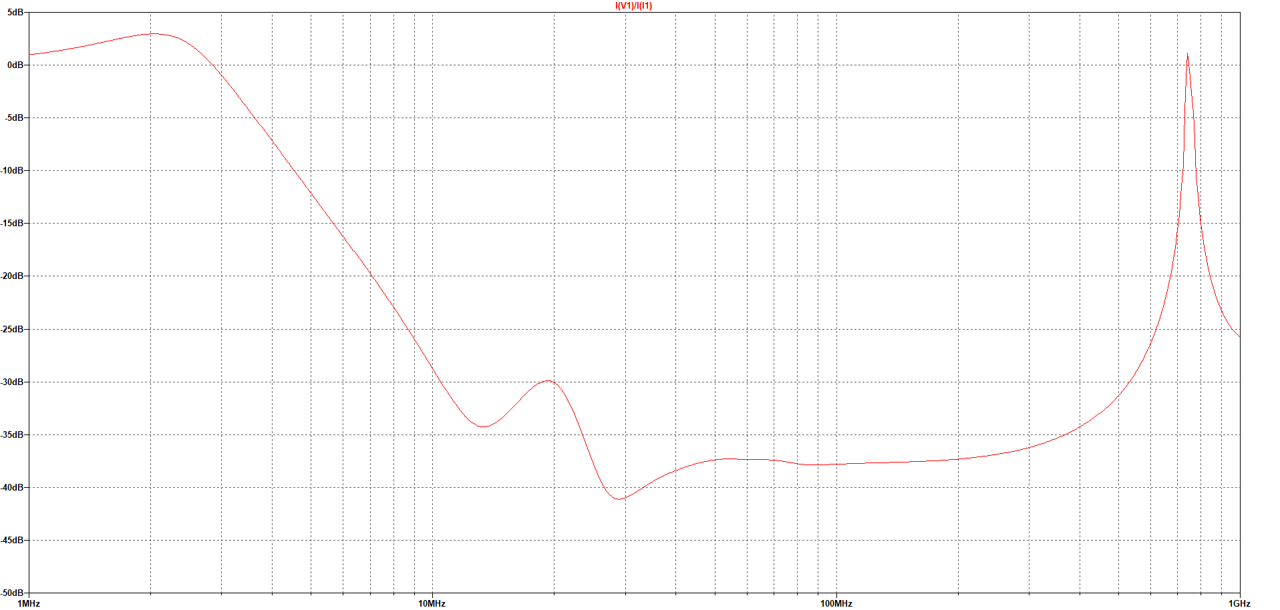

シミュレーション条件は、「AC Analysis」で 100points/Decade、1MHz~1GHzです。

解析結果

シミュレーション結果より、10MHz ~ 500MHzの範囲で30dBの減衰量が得られていることがわかります。

この周波数範囲については、半導体ICの動作周波数に対して基本波から5倍高調波までをカバーしていれば、ノイズ対策として十分機能すると判断することができます。

つまり、今回のデカップリング回路においては、動作周波数が10MHz~100MHzあたりまでであれば、十分なデカップリング性能が得られるということです。

パスコンの最適化

ここでは、0.1uFと1uFのコンデンサを組み合わせてデカップリング回路を構成しましたが、もちろんコンデンサ1つで減衰量を求めることも可能です。

それぞれ単体の減衰量と比較すると、減衰量や周波数範囲に違いが生じていることが確認できます。

出典:EMC設計イノベーション

出典:EMC設計イノベーションこのようにPD適用を活用することで、半導体ICごとにバイパスコンデンサの個数や定数を最適化することができます。

おわりに

今回は、PD適用を使ったデカップリング回路の設計方法について解説しました。

PD適用は、パワーインテグリティに通ずるデカップリング回路の設計手法で、LTSpiceを使ってパスコンをを最適化することができます。

回路設計段階におけるノイズ対策として非常に有用な手法なので、日頃からノイズ対策にお困りの方は是非チャレンジしてみてください。

なお今回の使用したシミュレーションファイルは以下よりダウンロードできます。

ダウンロードリンク

またPD適用の詳細については、EMC設計イノベーションのWEBサイトから確認できます。

PD適用に関する技術資料

今回は以上です。

最後まで読んでいただき、ありがとうございました。